[特殊字符]《计算机组成原理》第 8 章 - CPU 的结构和功能

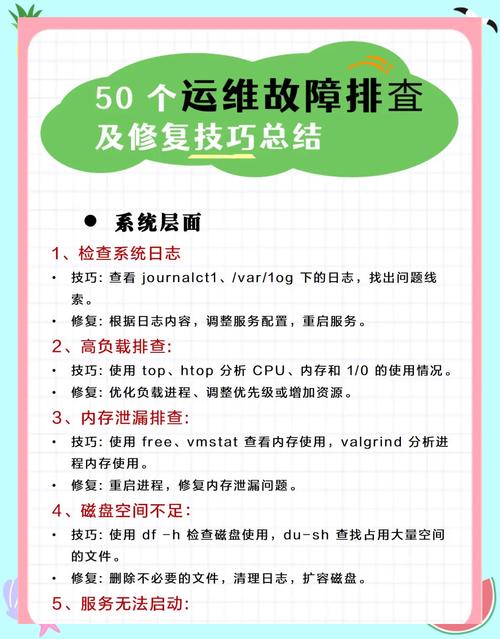

🔵8.1 CPU 的结构

🔵8.1.1 CPU 的功能

CPU(中央处理器)是计算机的核心部件,主要负责以下任务:

- 指令执行:解析并执行指令集架构(ISA)定义的指令

- 数据处理:完成算术运算(如加减乘除)和逻辑运算(如与或非)

- 存储控制:管理内存访问(读取 / 写入数据)

- 输入输出控制:协调 CPU 与外部设备的数据传输

- 中断处理:响应外部设备的异步请求

案例:简单算术运算实现

// 模拟CPU执行加法运算 public class SimpleCPU { // 通用寄存器 private int accumulator; // 累加器 private int registerB; // 通用寄存器B // 执行加法指令 public void addInstruction(int operand) { // 模拟取操作数到寄存器B registerB = operand; // 执行加法运算(累加器 + 寄存器B) accumulator += registerB; System.out.println("加法结果:" + accumulator); } public static void main(String[] args) { SimpleCPU cpu = new SimpleCPU(); cpu.addInstruction(5); // 初始累加器为0,执行0+5=5 cpu.addInstruction(3); // 执行5+3=8 } }🔵8.1.2 CPU 结构框图

图注:控制单元协调各部件工作,ALU 负责运算,寄存器组存储数据和地址

🔵8.1.3 CPU 的寄存器

分类及功能

寄存器类型 典型寄存器 功能描述 程序控制类 程序计数器 PC 存储下一条指令的内存地址 指令寄存器 IR 存储当前正在执行的指令 数据存储类 累加器 ACC 存放运算结果和待运算数据 通用寄存器 GR 临时存储数据(如 AX/BX/CX/DX 等) 状态控制类 状态寄存器 PSW 存储运算状态标志(如进位 / 溢出) 代码示例:寄存器操作模拟

// 模拟寄存器组操作 public class RegisterDemo { private int pc; // 程序计数器 private int ir; // 指令寄存器 private int acc; // 累加器 private int psw; // 状态寄存器(二进制位表示状态) // 模拟取指令操作 public void fetchInstruction(int address) { pc = address; // 设置PC到目标地址 ir = loadFromMemory(pc);// 从内存模拟函数获取指令 System.out.println("取指令:IR=" + ir); } private int loadFromMemory(int addr) { // 简化模拟:返回固定指令(假设0x1234为加法指令) return 0x1234; } }🔵8.1.4 控制单元和中断系统

控制单元功能

- 生成时序信号:控制指令执行的时序(时钟周期)

- 指令译码:解析 IR 中的指令操作码

- 发出控制信号:驱动 ALU、寄存器、内存等部件动作

中断系统核心概念

- 中断请求:外设通过中断线向 CPU 发送请求信号

- 中断响应:CPU 在当前指令执行结束后检测中断请求

- 中断服务:跳转至中断服务程序处理外设请求

🔵8.2 指令周期

🔵8.2.1 指令周期的基本概念

定义:执行一条指令所需要的全部时间,由若干机器周期(CPU 周期)组成

阶段划分:

- 取指周期:从内存读取指令到 IR

- 译码周期:分析指令操作码和寻址方式

- 执行周期:完成指令规定的操作

- 访存周期(可选):读写内存数据

- 中断周期(可选):处理中断请求

流程图:指令周期流程

🔵8.2.2 指令周期的数据流

示例:加法指令数据流

- PC → 内存地址总线(取指)

- 内存数据 → IR(指令存入 IR)

- PC 自增 → 指向下一条指令

- IR 操作码 → 控制单元译码

- 源操作数地址 → 内存 / 寄存器获取数据

- ALU 执行加法运算 → 结果存入 ACC

🔵8.3 指令流水

🔵8.3.1 指令流水原理

流水线思想:将指令执行过程分解为多个阶段(如取指 IF、译码 ID、执行 EX、访存 MEM、写回 WB),各阶段并行处理不同指令

示例:5 级流水线示意图

说明:每个时钟周期启动一条新指令,相邻指令在不同阶段并行执行

🔵8.3.2 影响流水线性能的因素

- 结构冲突:硬件资源竞争(如同时访问内存)

- 数据冲突:后续指令依赖前序指令的结果

- 控制冲突:分支指令导致流水线断流

🔵8.3.3 流水线性能

性能指标:

- 吞吐率(TP):单位时间执行的指令数

TP = n / (k + n - 1) * f(n 为指令数,k 为阶段数,f 为时钟频率)

- 加速比(S):流水线执行时间与非流水线执行时间的比值

🔵8.3.4 流水线中的多发技术

超标量技术

- 多个指令译码器和运算单元

- 示例:同时执行 2 条指令的流水线

// 模拟超标量流水线(简化版) public class SuperscalarPipeline { public void executeInParallel(Instruction inst1, Instruction inst2) { // 并行译码 decode(inst1); decode(inst2); // 并行执行(假设ALU1和ALU2独立) execute(inst1); execute(inst2); } private void decode(Instruction inst) { /* 译码逻辑 */ } private void execute(Instruction inst) { /* 执行逻辑 */ } } class Instruction { /* 指令类 */ }🔵8.3.5 流水线结构

典型流水线结构对比

流水线类型 阶段数 典型应用 简单流水线 3-5 级 早期 CPU(如 80486) 超流水线 6-15 级 Pentium 系列 乱序执行流水线 多级 现代 CPU(如酷睿) 🔵8.4 中断系统

🔵8.4.1 概述

中断分类:

- 硬件中断:来自外设(如键盘、磁盘)

- 软件中断:由指令触发(如系统调用)

- 异常:CPU 内部错误(如除法溢出)

中断处理流程:

- 中断请求 → 2. 中断判优 → 3. 中断响应 → 4. 中断服务 → 5. 中断返回

🔵8.4.2 中断请求标记和中断判优逻辑

数据结构模拟:中断请求寄存器

// 中断请求寄存器(8位,支持8个中断源) public class InterruptRequestRegister { private int irr; // 用整数模拟8位寄存器(每位代表一个中断源) // 设置中断请求(第n位设为1) public void setRequest(int n) { if (n >= 0 && n

免责声明:我们致力于保护作者版权,注重分享,被刊用文章因无法核实真实出处,未能及时与作者取得联系,或有版权异议的,请联系管理员,我们会立即处理! 部分文章是来自自研大数据AI进行生成,内容摘自(百度百科,百度知道,头条百科,中国民法典,刑法,牛津词典,新华词典,汉语词典,国家院校,科普平台)等数据,内容仅供学习参考,不准确地方联系删除处理! 图片声明:本站部分配图来自人工智能系统AI生成,觅知网授权图片,PxHere摄影无版权图库和百度,360,搜狗等多加搜索引擎自动关键词搜索配图,如有侵权的图片,请第一时间联系我们。

![[特殊字符]《计算机组成原理》第 8 章 - CPU 的结构和功能](https://i-blog.csdnimg.cn/direct/51f9b5c468b54b5493c05a03c52f0547.png)

![[特殊字符]《计算机组成原理》第 8 章 - CPU 的结构和功能](https://i-blog.csdnimg.cn/direct/7a7f907e91b5419984fd41545b56d70a.png)

![[特殊字符]《计算机组成原理》第 8 章 - CPU 的结构和功能](https://i-blog.csdnimg.cn/direct/6f26809be38a454a8d7d3cc59defaa0c.png)